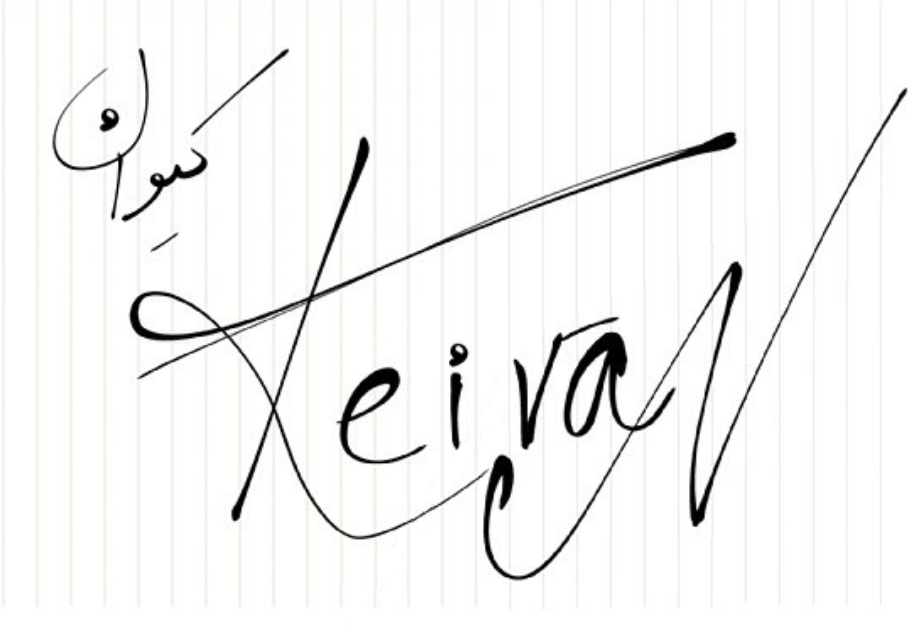

طراحی state

در این قسمت برای State Machine زیر یک برنامه طراحی خواهیم کرد

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity State is

Port ( clk1 : in STD_LOGIC;

clk2 : in STD_LOGIC;

x : in STD_LOGIC;

q : out STD_LOGIC_VECTOR (1 downto 0));

end State;

architecture Behavioral of State is

signal clk : STD_LOGIC;

signal p : STD_LOGIC_vector (1 downto 0);

signal st : integer range 0 to 3 := 0;

begin

process(clk1, clk2)

begin

if clk2'event and clk2 = '1' then

clk <= clk1;

end if;

end process;

process (clk)

begin

if clk = '1' and clk'event then

if st = 0 then

if x = '0' then

p <= "10";

st <= 2;

else

p <= "11";

st <= 3;

end if;

elsif st = 1 then

if x = '0' then

p <= "00";

st <= 0;

else

p <= "10";

st <= 2;

end if;

elsif st = 2 then

if x = '0' then

p <= "11";

st <= 3;

else

p <= "01";

st <= 1;

end if;

else

if x = '0' then

p <= "01";

st <= 1;

else

p <= "00";

st <= 0;

end if;

end if;

end if;

end process;

q <= not p;

end Behavioral;